RISC-V普通指令集

指令集架构(ISA)

指令是指处理器执行操作的最小单元。

指令集是一组指令的集合。

指令集架构(Instruction Set Architecture),有时简称为“架构”或“处理器架构”。有了指令集架构便可以使用不同的处理器硬件设计方案来实现不同性能的处理器。处理器的具体的硬件实现方案称为微架构(Microarchitecture)。虽然不同的的微架构实现会有成本与性能的差异,但软件无需做任何修改便可以运行在任何一款遵循同一指令集架构实现的处理器上。因此,指令集架构可以理解为一个抽象层,该抽象层构成处理器底层硬件与运行于其上的软件之间的接口。这也是计算机处理器中一个重要的抽象层。

RISC-V架构是一个基于精简指令集(RISC)原则的开源指令集架构(ISA),主要由美国加州大学伯克利分校的Krste Asanović、Andrew Waterman和Yunsup Lee等人于2010年推出。它支持32bit、64bit、128bit,采用小端序(Little-Endian)。

指令集

虽然RISC-V指令集架构(ISA)说起来很方便,但实际上RISC-V是一系列相关的指令集架构(ISA)家族。目前这个家族中有四种基础的指令集架构(ISA)。

而一个RISC-V ISA由一个基本整数指令集架构(ISA)和一系列可选的扩展指令集架构(ISA)组成。

基本指令集

| 版本 | 状态 | 指令数 | 描述 | |

|---|---|---|---|---|

| RV32I | 2.1 | 冻结 | 47 | 支持32个寄存器、32位地址空间、32位整数指令 |

| RV64I | 2.1 | 冻结 | 59 | 支持32个寄存器、64位地址空间、64及一部分32位整数指令 |

| RV128I | 1.7 | 开放 | 71 | 支持32个寄存器、128位地址空间、128及一部分64和32位整数指令 |

| RV32E | 1.9 | 开放 | 47 | 支持16个寄存器、32位地址空间、32位整数指令 |

扩展指令集

只列出几个常用的扩展指令集

| 版本 | 状态 | 指令数 | 描述 | |

|---|---|---|---|---|

| M | 2.0 | 冻结 | 8 | 整数乘法、除法 |

| A | 2.1 | 冻结 | 11 | 存储器原子操作指令和Load-Reserved/Store-Conditional指令 |

| F | 2.2 | 冻结 | 26 | 单精度32bit浮点指令 |

| D | 2.2 | 冻结 | 26 | 双精度64bit浮点指令,必须支持扩展指令集F |

| C | 2.0 | 冻结 | 46 | 压缩指令,指令长度为16位 |

特别说明,“通用”指令集名G代表了IMAFD的组合。

其它扩展指令

| 状态 | 描述 | |

|---|---|---|

| Q | 冻结 | 四倍精确度浮点运算标准扩展 |

| L | 开放 | 十进制浮点运算标准扩展 |

| B | 开放 | 位操作标准扩展 |

| J | 开放 | 动态指令翻译标准扩展 |

| T | 开放 | 顺序存储器访问标准扩展 |

| P | 开放 | 单指令多资料流(SIMD)运算标准扩展 |

| V | 开放 | 向量运算标准扩展 |

| N | 开放 | 用户中断标准扩展 |

指令编码

基本的RISC-V指令集架构(ISA)的指令长度固定为32bit,而且必需在32bit边界上自然对齐。

但标准的RISC-V编码机制在设计的时候旨在支持具有可变长度指令的ISA扩展。其每一条指令长度可以是16bit的任意倍数,并且在16bit边界上自然对齐。

标准的压缩扩展ISA(C),提供压缩的16bit指令以缩减代码的大小,并放宽指令的对齐约束,允许所有指令(16bit和32bit)在任意的16bit边界上对齐,以提高代码密码。

RISC-V的指令只有两种对齐方式,要么是按16bit对齐,要么是按32bit对齐。

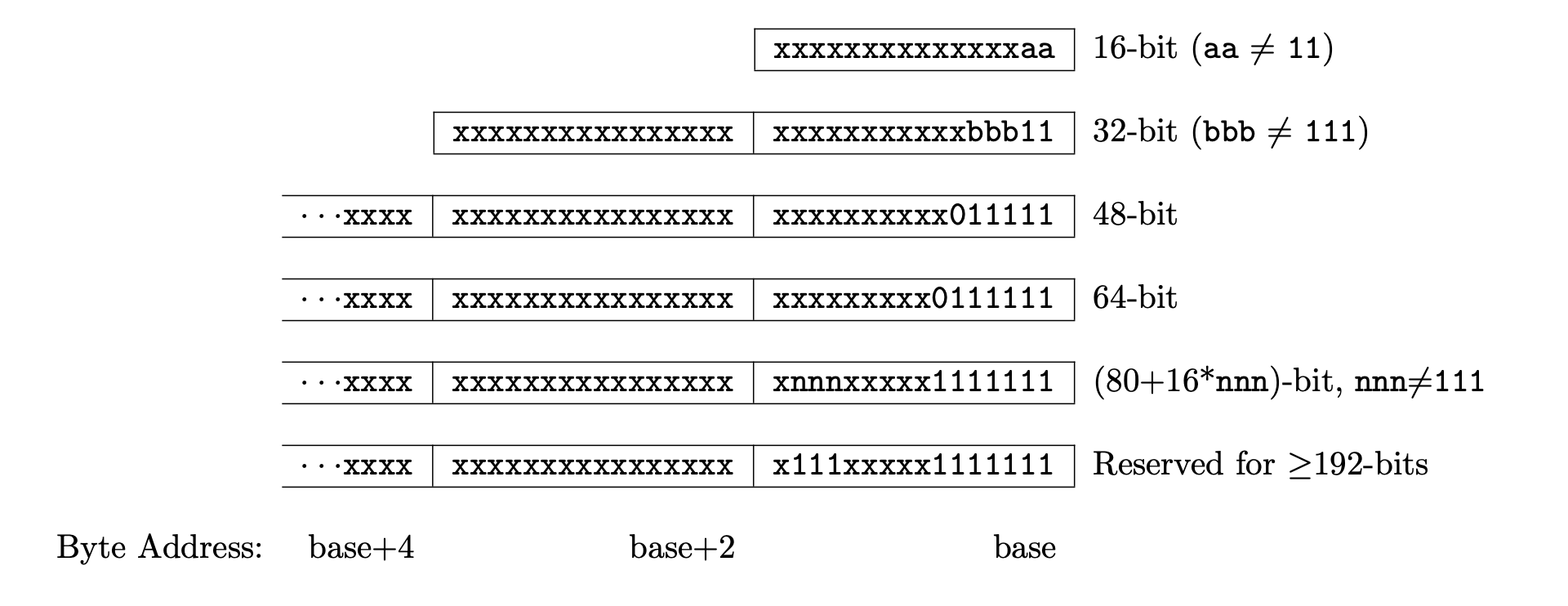

扩展指令长度编码

32位指令的编码空间的一部分暂时分配给了超过32位的指令。目前这个空间是保留状态,并且超过32位的指令提议还处于未冻结状态。

可选的压缩16位指令集扩展的最低两位为00、01或10。

所有在基本指令集架构中的32位指令的最低两位都为11。

最低6位为011111的表示是48位指令集,最低7位为0111111的表示是64位指令集。

80位到176位指令则使用bits[14:12]来编码,当bits[14:12]全为1则是为长度>=192位保留的。

目前仅16bit和32bit编码已经冻结。

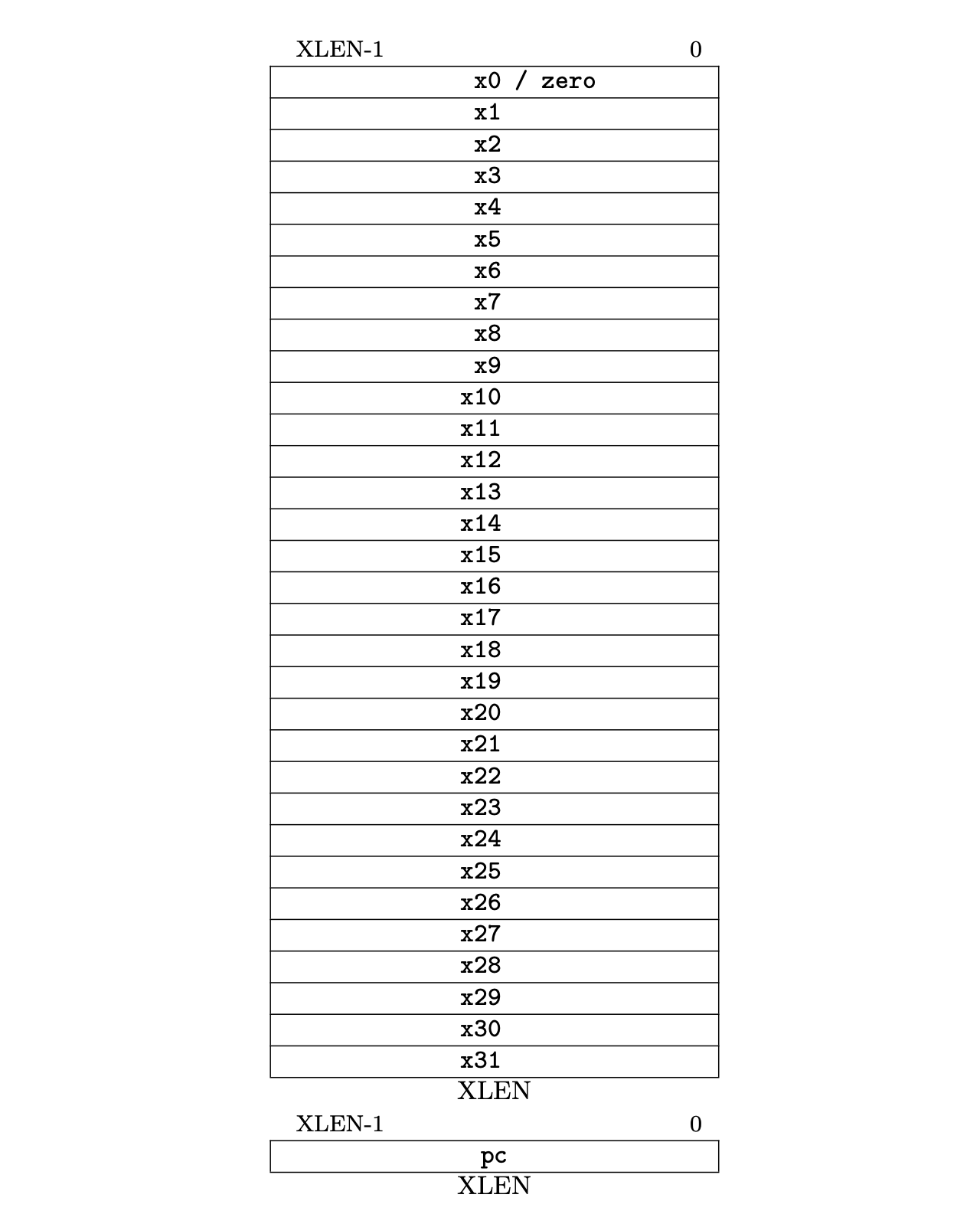

寄存器

RISC-V处理器有32个通用寄存器(RV32E只有16个):x0~x31。其中x0的值恒为0。

通用寄存器x1~x31保存各种指令解释为一组布尔值的值,或作为二进制补码的有符号数,或无符号的二进制数。

除此之外,还有一个普通寄存器:程序计数器pc用于保存当前指令的地址。

对于RV32I、RV32E来说XLEN == 32,对于RV64I来说XLEN == 64。

在基本的整数指令集架构(ISA)中没有专用的栈指针寄存器和子程序返回地址链接寄存器,因为指令编码允许将任何x寄存器用于此目的。但是标准的软件调用约定使用寄存器x1来保存调用的返回地址,寄存器x2用于堆栈指针寄存器,寄存器x5用于备用链接寄存器。

通用寄存器

| Register | ABI Name | Description | Saver |

|---|---|---|---|

x0 |

zero |

Hard-wired zero | – |

x1 |

ra |

Return address | Caller |

x2 |

sp |

Stack pointer | Callee |

x3 |

gp |

Global pointer | – |

x4 |

tp |

Thread pointer | – |

x5 |

t0 |

Temporary/alternate link register | Caller |

x6-7 |

t1-2 |

Temporaries | Caller |

x8 |

s0/fp |

Saved register/frame pointer | Callee |

x9 |

s1 |

Saved register | Callee |

x10-11 |

a0-1 |

Function arguments/return values | Caller |

x12-17 |

a2-7 |

Function arguments | Caller |

x18-27 |

s2-11 |

Saved register | Callee |

x28-31 |

t3-6 |

Temporaries | Caller |

浮点寄存器

| Register | ABI Name | Description | Saver |

|---|---|---|---|

f0-7 |

ft0-7 |

FP temporaries | Caller |

f8-9 |

fs0-1 |

FP saved registers | Callee |

f10-11 |

fa0-1 |

FP arguments/return values | Caller |

f12-17 |

`fa2-7 |

FP arguments | Caller |

f18-27 |

fs2-11 |

FP saved registers | Callee |

f28-31 |

ft8-11 |

FP temporaries | Caller |